# AMP DISPLAY INC.

# **SPECIFICATIONS**

# 2.0 TFT MODULE

| CUSTOMER:               |                                               |      |

|-------------------------|-----------------------------------------------|------|

| CUSTOMER PART NO.       |                                               |      |

| AMP DISPLAY PART<br>NO. | AM-176220C2TMQW-00                            | Н    |

| APPROVED BY:            |                                               |      |

| DATE:                   |                                               |      |

|                         | OR SPECIFICATIONS OR SPECIFICATION AND PROTOT | YPES |

# **AMP DISPLAY INC**

9856 SIXTH STREET RANCHO CUCAMONGA CA 91730 TEL: 909-980-13410 FAX: 909-980-1419 WWW.AMPDISPLAY.COM

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

# RECORD OF REVISION

| <b>Revision Date</b> | Page | Contents    | Editor |

|----------------------|------|-------------|--------|

| 2006/12/27           | -    | New Release | Edward |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

|                      |      |             |        |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

### 1 Features

This single-display module is suitable for cellphone application. The Main-LCD adopts one backlight with High brightness 3-lamps white LED.

- (1) Main LCD: 1.1 Amorphous-TFT 2.0 inch display, Transmissive, Positive type, Normally white type, 6 o'clock.

- 1.2 176(RGB)X220 dots Matrix, 1/220 Duty.

- 1.3 Narrow-contact ledge technique.

- 1.4 Main LCD Driver IC: HX8306A

- 1.5 Full 262K colors display.

Back ground : black (Back-Light, Red, Green, Blue dots are off state)

- (2) Low cross talk by frame rate modulation

- (3) Direct data display with display RAM

- (4) Partial display function: You can save power by limiting the display space.

- (5) MPU interface: 8bit/16bit/80Serial, parallel interface.

- (6) 18-bit bus RGB interface.

- (7) Abundant command functions:

Area scroll function

Display direction switching function

Power saving function

Electric volume control function: you are able to program the temperature compensation function.

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

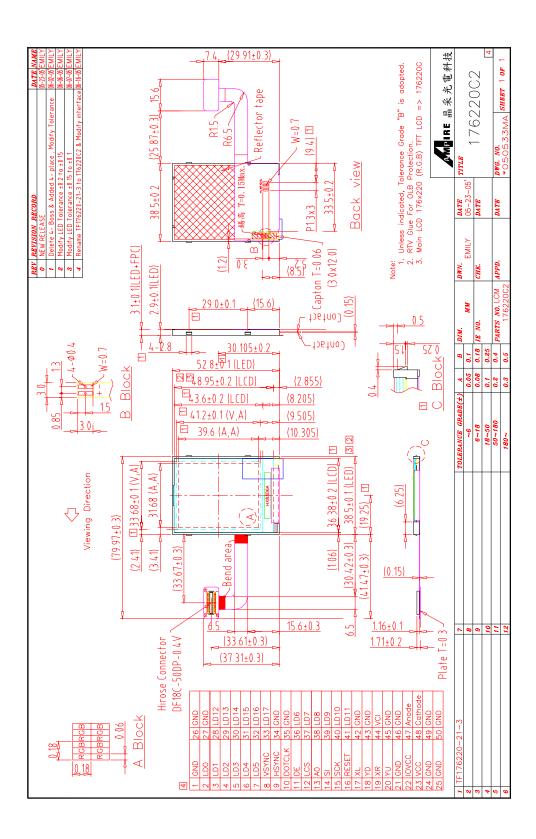

# 2 Mechanical specifications

### Dimensions and weight

| Item                      |              | Specifications                | Unit |

|---------------------------|--------------|-------------------------------|------|

| External shape dimensions |              | *80(W) x 53(H) x 3.2 (D) Max. | mm   |

| Main                      | Pixel pitch  | 0.180 (W) x 0.180(H)          | mm   |

| LCD                       | Active area  | 31.68 (W) x 39.6 (H)          | mm   |

| LOD                       | Viewing area | 33.68 (W) x 41.2 (H)          | mm   |

| Weight                    |              | T.B.D                         | g    |

<sup>\*1.</sup> This specification is about External shape on shipment from AMPIRE.

# 3 Absolute max. ratings and environment

### 3-1 Absolute max. ratings

Ta=25°C GND=0V

| Item          | Symbol        | Min. | Max.    | Unit | Remarks |

|---------------|---------------|------|---------|------|---------|

| Power voltage | VDD – GND     | -0.3 | +4.0    | V    |         |

| Power voltage | LED A – LED K | -0.5 | +12.8   | V    |         |

| Input voltage | VIN           | -0.5 | VDD+0.5 | V    |         |

### 3-2 Environment

| Item                  | Specifications          | Remarks                   |

|-----------------------|-------------------------|---------------------------|

| Storage temperature   | Max. +80 °C<br>Min30 °C | Note 1:<br>Non-condensing |

| Operating temperature | Max. +70 °C<br>Min20 °C | Note 1:<br>Non-condensing |

Note 1: Ta≤+40 °C · · · Max.85%RH

Ta>+40  $^{\circ}$ C · · · The max. humidity should not exceed the humidity with 40  $^{\circ}$ C 85%RH.

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

# 4 Electrical specifications

### 4-1 Electrical characteristics of LCM

$(V_{DD}=3.0V, Ta=25 \,{}^{\circ}C)$

| Item                       | Symbol              | Conditions                 | MIN.               | TYP. | MAX.               | Unit |

|----------------------------|---------------------|----------------------------|--------------------|------|--------------------|------|

| IC power voltage           | $V_{DD}$            |                            | 2.4                | 3.0  | 3.6                | V    |

| High-level input voltage   | V <sub>IHC</sub>    |                            | 0.8V <sub>DD</sub> |      | $V_{DD}$           | V    |

| Low-level input voltage    | V <sub>ILC</sub>    |                            | 0                  |      | 0.2V <sub>DD</sub> | V    |

| Consumption current of VDD | I <sub>DD</sub>     | LED OFF                    | -                  | 4    |                    | mA   |

| Consumption current of LED | I <sub>LED_ON</sub> | V <sub>LED_ON</sub> =12.0V | -                  | 15   | 20                 | mA   |

<sup>1. 1/220</sup> duty.

2. Electronic Volumn value: (xxxxh) Decimal

3. Thermal Gradient: -0.05%/°C

4. Range of Electronic Volumn control : (xxxxH±3) Decimal

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

# 4-2 LED back light specification

| Item                        | Symbol                   | Conditions           | MIN.  | TYP. | MAX. | Unit              |

|-----------------------------|--------------------------|----------------------|-------|------|------|-------------------|

| Forward voltage             | $V_{f}$                  | I <sub>f</sub> =15mA | 9.3   | 9.8  | 10.8 | V                 |

| Reverse voltage             | V <sub>r</sub>           |                      | -     | -    | 12   | V                 |

| Forward current             | I <sub>f</sub>           | 3-chip serial        | 12    | 15   | 20   | mA                |

| Power Consumption           | $P_{BL}$                 | I <sub>f</sub> =15mA | -     | 162  | -    | mW                |

| Uniformity (with L/G)       | -                        | I <sub>f</sub> =15mA | 80%*1 | -    | -    |                   |

| Bare LED Luminous intensity | V <sub>f</sub>           | 9.8V<br>15mA         | 2400  | -    | -    | cd/m <sup>2</sup> |

| Luminous color              | White                    |                      |       |      |      |                   |

| Chip connection             | 3 chip serial connection |                      |       |      |      |                   |

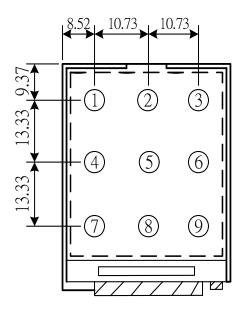

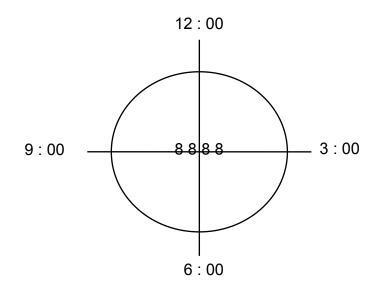

## Bare LED measure position:

\*1 Uniformity (LT):

$$\frac{Min(P1 \sim P9)}{Max(P1 \sim P9)} \times 100 \ge 80\%$$

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

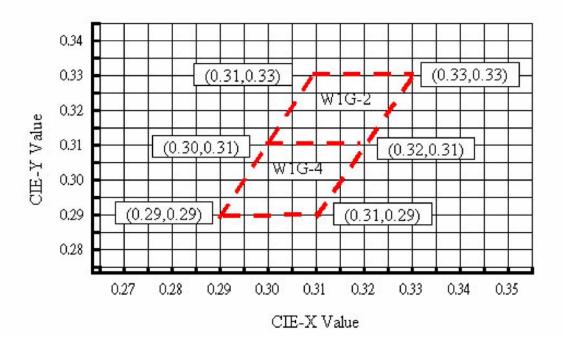

# 4.3 CIE, Brightness, and Vf Classification

CIE, Brightness, and Vf Classification (at 20mA)

|       | CIE(X,Y)                                                      | Brightness (Iv)                    | Vf                                  |

|-------|---------------------------------------------------------------|------------------------------------|-------------------------------------|

| W1G-2 | (0.31, 0.33) – (0.33, 0.33) -<br>(0.30, 0.31) – (0.32,0.31) - | 1000 ~ 1100 mcd                    | 3.0 ~ 3.1<br>3.1 ~ 3.2<br>3.2 ~ 3.3 |

| W1G-4 | (0.30, 0.31) – (0.32,0.31) -<br>(0.29, 0.29) – (0.31,0.29) -  | 1100 ~ 1200 mcd<br>1200 ~ 1300 mcd | 3.3 ~ 3.4<br>3.4 ~ 3.5<br>3.5 ~ 3.6 |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

# 5 Optical characteristics

### **Main LCD**

5.1 Optical characteristics

$(1/220 \text{ Duty in case except as specified elsewhere Ta = }25^{\circ}\text{C})$

### LED backlight transmissive module:

| lto.mo                            | Cymahal | Taman | Min  | Ctd                                  | Max  | l lm:#      | Conditions                                     |

|-----------------------------------|---------|-------|------|--------------------------------------|------|-------------|------------------------------------------------|

| Item                              | Symbol  | Temp. | Min. | Std.                                 | Max. | Unit        | Conditions                                     |

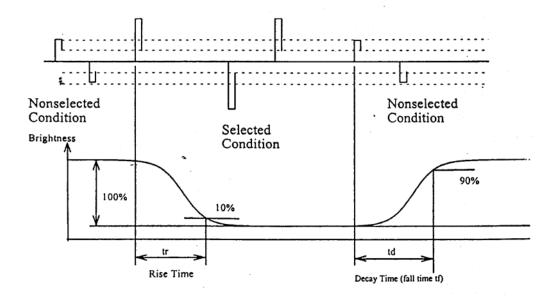

| Response                          | Tr      | 25 °C | -    | 15                                   | 30   | mo          | $\theta$ =0 ° , $\varphi$ =0 °                 |

| time                              | Tf      | 25 °C | -    | 30                                   | 50   | ms          | (Note 2)                                       |

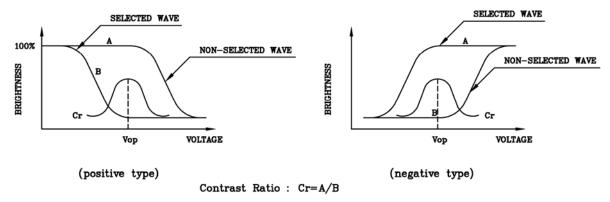

| Contrast ratio                    | CR      | 25 °C | 200  | -                                    | -    | -           | $\theta = 0^{\circ},  \varphi = 0^{\circ}$     |

| Transmittance                     | Т       | 25 °C | -    | 6.7                                  | -    | %           |                                                |

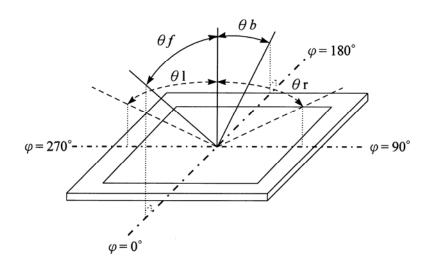

| Visual angle range front and rear | θ       | 25 °C |      | ( θ f) 45<br>( θ b) 15               |      | De-<br>gree | φ = 0°, CR ≥ 10<br>(Note 3)                    |

| Visual angle range left and right | θ       | 25 °C |      | ( <i>θ</i> I) 50<br>( <i>θ</i> r) 45 |      | De-<br>gree | φ =90°, CR≧10<br>(Note 3)                      |

| Visual angle direction priority   |         |       |      | 6:00                                 |      |             | (Note 5)                                       |

| Brightness                        |         |       |      | 200                                  |      | Cd/<br>m2   | V <sub>LED</sub> =12V, 15mA Full White pattern |

# 5.2 CIE (x, y) chromaticity (1/220 Duty Ta = $25^{\circ}$ C)

| Item  | Symbol | -      | Transmissive | Conditions |                                              |

|-------|--------|--------|--------------|------------|----------------------------------------------|

| item  | Cymbol | Min.   | Std.         | Max.       | Conditions                                   |

| Red   | х      | 0.5339 | 0.5839       | 0.6339     | $\theta = 0^{\circ}$ , $\varphi = 0^{\circ}$ |

|       | У      | 0.3128 | 0.3628       | 0.4128     | - 7,                                         |

| Green | Х      | 0.3005 | 0.3505       | 0.4005     | $\theta = 0^{\circ}$ , $\varphi = 0^{\circ}$ |

| 0.00  | У      | 0.5403 | 0.5903       | 0.6403     | ,,                                           |

| Blue  | х      | 0.0969 | 0.1469       | 0.1969     | $\theta = 0^{\circ}$ , $\varphi = 0^{\circ}$ |

| 2.00  | У      | 0.0927 | 0.1427       | 0.1927     | , ,                                          |

|       | Х      | 0.2820 | 0.3320       | 0.3820     | $\theta = 0^{\circ}$ , $\varphi = 0^{\circ}$ |

| White | У      | 0.3111 | 0.3611       | 0.4111     | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,      |

|       | L      | 200    | -            | -          | $\theta = 0^{\circ}$ , $\varphi = 0^{\circ}$ |

| Black | L      | 0.5    | -            | 1.2        | $\theta$ =0° , $\varphi$ =0°                 |

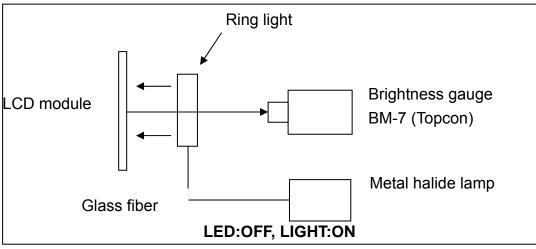

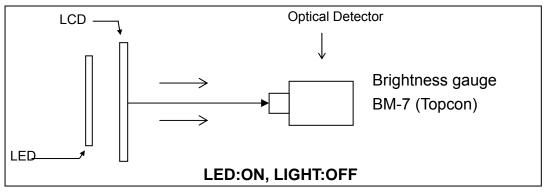

**NOTE 1: Optical characteristic measurement system**

**NOTE 2: Response tome definition**

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

NOTE 3:  $\varphi \cdot \theta$  definition

**NOTE 4: Contrast definition**

**NOTE 5: Visual angle direction priority**

10

Date: 2006/12/27 AMPIRE CO., LTD.

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

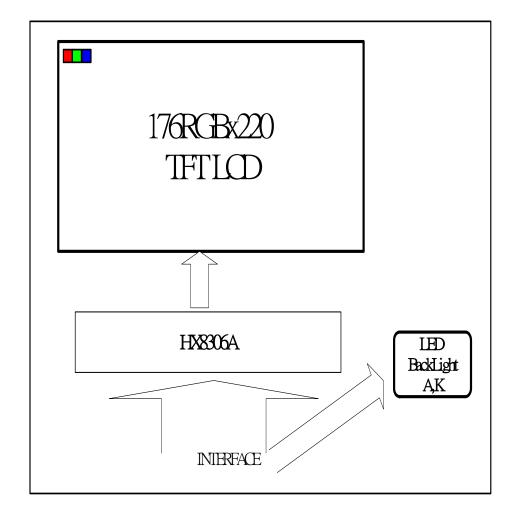

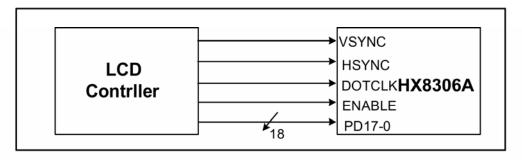

# 6 Block Diagram

# **Block diagram (Main LCD)**

Display format: A-Si TFT transmissive, Normally white type, 6 o'clock.

Display composition: 176 x RGB x 220 dots

LCD Driver: HX8306A

Back light: White LED x 3 ( $I_{LED}$ =15mA)

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

# 7 Interface specifications

| Pin No. | Terminal | Functions                                                                                                                                                                            |  |  |  |

|---------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1       | GND      | GND-terminal for analog circuit                                                                                                                                                      |  |  |  |

| 2       | LD0      |                                                                                                                                                                                      |  |  |  |

| 3       | LD1      |                                                                                                                                                                                      |  |  |  |

| 4       | LD2      | 18-bits RGB Interface Circuit                                                                                                                                                        |  |  |  |

| 5       | LD3      | TO She responded on our                                                                                                                                                              |  |  |  |

| 6       | LD4      |                                                                                                                                                                                      |  |  |  |

| 7       | LD5      |                                                                                                                                                                                      |  |  |  |

| 8       | VSYNC    | Frame synchronizing signal in RGB I/F mode.                                                                                                                                          |  |  |  |

| 9       | HSYNC    | Frame synchronizing signal in RGB I/F mode.                                                                                                                                          |  |  |  |

| 10      | DOTCLK   | Dot clock signal in RGB I/F mode.                                                                                                                                                    |  |  |  |

| 11      | DE       | A data ENABLE signal in RGB I/F mode.                                                                                                                                                |  |  |  |

| 12      | LCS      | Main LCD chip select at low.                                                                                                                                                         |  |  |  |

| 13      | Α0       | <ol> <li>Command / data select input terminal. Data with "H," and command with "L".</li> <li>Connect to VCC or GND level when serial data transfer interface is selected.</li> </ol> |  |  |  |

| 14      | SDI      | When Serial Data Input pin in Serial Data Transfer interface. The input data is latched by the rising edge of the SCL signal on the chip. series MPU                                 |  |  |  |

| 15      | E_NWR    | Serves as a write signal and writes data at the rising edge in i80 system interface.  Serves as the synchronous clock signal in serial data transfer interface.                      |  |  |  |

| 16      | RESET    | Reset pin. Setting either pin low initializes the LSI. Must be reset after power is supplied.                                                                                        |  |  |  |

| 17      | XL       |                                                                                                                                                                                      |  |  |  |

| 18      | YD       |                                                                                                                                                                                      |  |  |  |

| 19      | XR       | Touch panel pad.                                                                                                                                                                     |  |  |  |

| 20      | YU       |                                                                                                                                                                                      |  |  |  |

| 21      | GND      | GND-terminal for analog circuit                                                                                                                                                      |  |  |  |

| 22      | IOVCC    | Power supply for internal core logic when VDC is disabled. Voltage range: 1.65 ~ 3.3V if VDC is disabled. Tie together with VCC if VDC is enabled.                                   |  |  |  |

| 23      | VCC      | Power input terminal (System Power).                                                                                                                                                 |  |  |  |

| 24      | GND      |                                                                                                                                                                                      |  |  |  |

| 25      | GND      |                                                                                                                                                                                      |  |  |  |

| 26      | GND      | GND-terminal for analog circuit                                                                                                                                                      |  |  |  |

| 27      | GND      |                                                                                                                                                                                      |  |  |  |

Date: 2006/12/27 AMPIRE CO., LTD.

| 28 | LD12    |                                                                                 |  |  |  |  |  |

|----|---------|---------------------------------------------------------------------------------|--|--|--|--|--|

| 29 | LD13    |                                                                                 |  |  |  |  |  |

| 30 | LD14    | 18-bits RGB Interface Circuit                                                   |  |  |  |  |  |

| 31 | LD15    | 18-bits RGB interface Circuit                                                   |  |  |  |  |  |

| 32 | LD16    |                                                                                 |  |  |  |  |  |

| 33 | LD17    |                                                                                 |  |  |  |  |  |

| 34 | GND     | OND to order to a section of                                                    |  |  |  |  |  |

| 35 | GND     | GND-terminal for analog circuit                                                 |  |  |  |  |  |

| 36 | LD6     |                                                                                 |  |  |  |  |  |

| 37 | LD7     |                                                                                 |  |  |  |  |  |

| 38 | LD8     | 18-bits RGB Interface Circuit                                                   |  |  |  |  |  |

| 39 | LD9     | To-DIS RGB IIILEHACE CITCUIL                                                    |  |  |  |  |  |

| 40 | LD10    |                                                                                 |  |  |  |  |  |

| 41 | LD11    |                                                                                 |  |  |  |  |  |

| 42 | GND     | GND-terminal for analog circuit                                                 |  |  |  |  |  |

| 43 | GND     | GND-terminal for analog circuit                                                 |  |  |  |  |  |

| 44 | VCI     | For analog circuit power supply. Connect to an external power supply 2.5V~3.3V. |  |  |  |  |  |

| 45 | GND     | CND terminal for analog circuit                                                 |  |  |  |  |  |

| 46 | GND     | GND-terminal for analog circuit                                                 |  |  |  |  |  |

| 47 | ANODE   | LED Backlight A terminal                                                        |  |  |  |  |  |

| 48 | CATHODE | LED Backlight K terminal                                                        |  |  |  |  |  |

| 49 | GND     | GND-terminal for analog circuit                                                 |  |  |  |  |  |

| 50 | GND     | OND-terminal for analog circuit                                                 |  |  |  |  |  |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

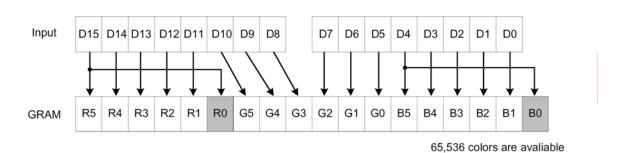

# 7.1 System interface

### **Serial Data Transfer Interface**

Data Format of Serial Data Transfer Interface GRAM

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

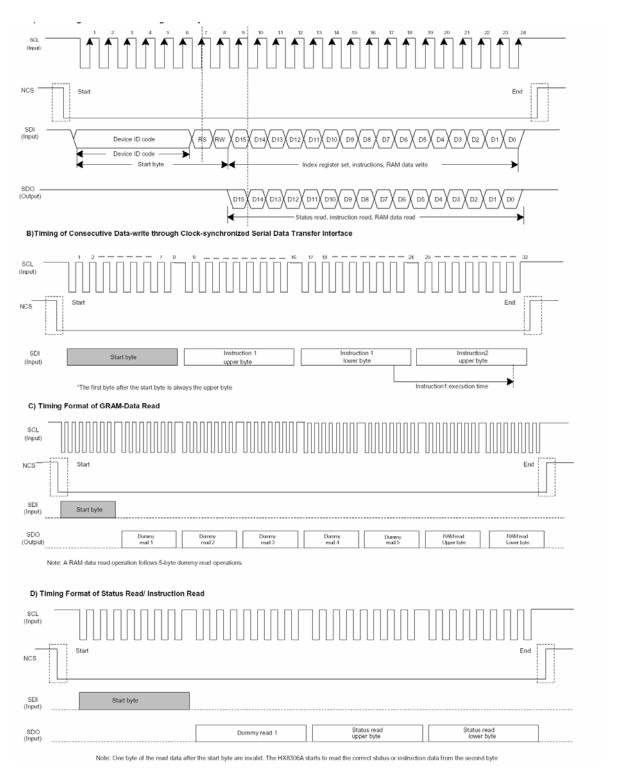

# **Basic Timing Transfer Format through Clock-Synchronized Serial Data Transfer Interface**

Data transfer through Serial Data Transfer Interface

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

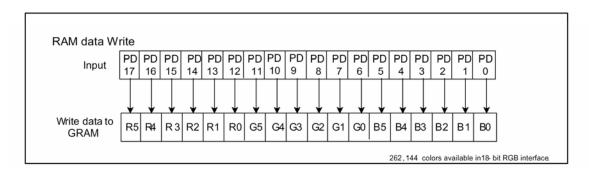

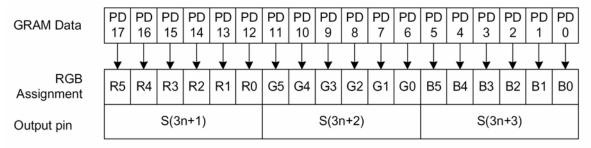

### 7.2 18-bit bus RGB interface

Example of 18-bit bus Interface

18-bit RGB interface

Data format for 18-bit interface

Note: n = lower eight bits of address (0 to 175)

GRAM data and display data: RGB interface (SS= "0", RGB= "0")

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

# **INSTRUCTION DESCRIPTIONS**

# 7.3 Instruction List

| Reg. | Pagiotar                  | R/W  | RS |             |             |             | Upper       | Code        | )           |             |             |            |             |             | Lower       | Code        |             |             |             |

|------|---------------------------|------|----|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| No.  | Register                  | K/VV | Ko | RB15        | RB14        | RB13        | RB12        | RB11        | RB10        | RB9         | RB8         | RB7        | RB6         | RB5         | RB4         | RB3         | RB2         | RB1         | RB0         |

| IR   | Index                     | 0    | 0  | *           | *           | *           | *           | *           | *           | *           | *           | *          | ID6         | ID5         | ID4         | ID3         | ID2         | ID1         | ID0         |

| SR   | Status read               | 1    | 0  | L7          | L6          | L5          | L4          | L3          | L2          | L1          | L0          | 0          | 0           | 0           | 0           | 0           | 0           | 0           | 0           |

| R00h | Oscillation Start         | 0    | 1  | *           | *           | *           | *           | *           | *           | *           | *           | *          | *           | *           | *           | *           | *           | *           | 1           |

| Roon | Device code read          | 1    | 1  | 0           | 0           | 0           | 0           | 0           | 1           | 1           | 1           | 1          | 0           | 0           | 0           | 1           | 0           | 0           | 1           |

| R01h | Driver output control     | 0    | 1  | 0           | VSPL<br>(0) | SHP<br>L(0) | DPL<br>(0)  | EPL<br>(0)  | SM<br>(0)   | GS<br>(0)   | SS<br>(0)   | 0          | 0           | 0           | NL4<br>(1)  | NL3<br>(1)  | NL2<br>(1)  | NL1<br>(0)  | NL0<br>(1)  |

| R02h | LCD drive AC control      | 0    | 1  | 0           | 0           | 0           | 0           | FLD<br>(0)  | FLD0<br>(1) | B/C<br>(0)  | EOR<br>(0)  | 0          | 0           | NW5<br>(0)  | NW4<br>(0)  | NW3<br>(0)  | NW2<br>(0)  | NW1<br>(0)  | NW0<br>(0)  |

| R03h | Entry mode                | 0    | 1  | TPI<br>(0)  | DFM<br>1(0) | DFM<br>0(0) | BGR<br>(0)  | 0           | 0           | HWM<br>(0)  | 0           | 0          | 0           | ID1<br>(1)  | ID0<br>(1)  | AM<br>(0)   | LG2<br>(0)  | LG1<br>(0)  | LG0<br>(0)  |

| R04h | Compare register (1)      | 0    | 1  | 0           | 0           | CP11<br>(0) | CP10<br>(0) | CP9<br>(0)  | CP8<br>(0)  | CP7<br>(0)  | CP6<br>(0)  | 0          | 0           | CP5<br>(0)  | CP4<br>(0)  | CP3<br>(0)  | CP2<br>(0)  | CP1<br>(0)  | CP0<br>(0)  |

| R05h | Compare register (2)      | 0    | 1  | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0          | 0           | CP17<br>(0) | CP16<br>(0) | CP15<br>(0) | CP14<br>(0) | CP13<br>(0) | CP12<br>(0) |

| R06h |                           |      |    |             |             |             |             |             |             |             |             |            |             |             |             |             |             |             |             |

| R07h | Display control(1)        | 0    | 1  | 0           | 0           | 0           | PT1 (0)     | PT0<br>(0)  | VLE2<br>(0) | VLE1<br>(0) | SPT<br>(0)  | 0          | 0           | GON<br>(0)  | DTE<br>(0)  | CL<br>(0)   | REV<br>(0)  | D1<br>(0)   | D0<br>(0)   |

| R08h | Display control(2)        | 0    | 1  | 0           | 0           | 0           | 0           | FP3<br>(1)  | FP2<br>(0)  | FP1<br>(0)  | FP0<br>(0)  | 0          | 0           | 0           | 0           | BP3<br>(1)  | BP2<br>(0)  | BP1<br>(0)  | BP0<br>(0)  |

| R09h | Display control(3)        | 0    | 1  | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0          | 0           | PTG<br>1(0) | PTG<br>0(0) | ISC3<br>(0) | ISC2<br>(0) | ISC1<br>(0) | ISC0<br>(0) |

| R0Ah |                           |      |    |             |             |             |             |             |             |             |             |            |             |             |             |             |             |             |             |

| R0Bh | Frame cycle control       | 0    | 1  | NO1<br>(0)  | NO0<br>(0)  | SDT1<br>(0) | SDT0<br>(0) | EQ1<br>(0)  | EQ0<br>(0)  | DIV1<br>(0) | DIV0<br>(0) | 0          | 0           | 0           | 0           | RTN3<br>(0) | RTN2<br>(0) | RTN1<br>(0) | RTN0<br>(0) |

| R0Ch | Extemal Display control   | 0    | 1  | 0           | 0           | 0           | 0           | 0           | 0           | 0           | RM<br>(0)   | 0          | 0           | DM1<br>(0)  | DM0<br>(0)  | 0           | 0           | RIM1<br>(0) | RIM0<br>(0) |

| R10h | Power control (1)         | 0    | 1  | 0           | SAP2<br>(0) | SAP1<br>(0) | SAP0<br>(0) | 0           | BT2<br>(0)  | BT1<br>(0)  | BT0<br>(0)  | 0          | AP2<br>(0)  | AP1<br>(0)  | AP0<br>(0)  | 0           | DK<br>(1)   | SLP<br>(0)  | STB (0)     |

| R11h | Power control (2)         | 0    | 1  | 0           | 0           | 0           | 0           | 0           | DC12<br>(0) | DC11<br>(0) | DC10<br>(0) | 0          | DC02<br>(0) | DC01<br>(0) | DC00<br>(0) | 0           | VC2<br>(0)  | VC1<br>(0)  | VC0<br>(0)  |

| R12h | Power control (3)         | 0    | 1  | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0          | 0           | 0           | PON<br>(0)  | VRH<br>3(0) | VRH<br>2(0) | VRH<br>1(0) | VRH<br>0(0) |

| R13h | Power control (4)         | 0    | 1  | 0           | 0           | VCO<br>MG   | VDV<br>4(0) | VDV<br>3(0) | VDV<br>2(0) | VDV<br>1(0) | VDV<br>0(0) | 0          | 0           | 0           | VCM<br>4(0) | VCM<br>3(0) | VCM<br>2(0) | VCM<br>1(0) | VCM<br>0(0) |

| R21h | Vertical scroll control   | 0    | 1  | AD15<br>(0) | AD14<br>(0) | AD13<br>(0) | AD12<br>(0) | AD11<br>(0) | AD10<br>(0) | AD9<br>(0)  | AD8<br>(0)  | AD7<br>(0) | AD6<br>(0)  | AD5<br>(0)  | AD4<br>(0)  | AD3<br>(0)  | AD2<br>(0)  | AD1<br>(0)  | AD0<br>(0)  |

| R22H | RAM data<br>write/ read   | 0    | 1  |             | V           | /rite/ F    | Read        | Data        | (Uppe       | r)          |             |            | ٧           | Vrite/ I    | Read        | Data (      | Lower       | -)          |             |

| R23h | RAM Write data<br>Mask(1) | 0    | 1  | 0           | 0           | WM1<br>1(0) | WM1<br>0(0) | WM9<br>(0)  | WM8<br>(0)  | WM7<br>(0)  | WM6<br>(0)  | 0)         | 0           | WM5<br>(0)  | WM4<br>(0)  | WM3<br>(0)  | WM2<br>(0)  | WM1<br>(0)  | WM0<br>(0)  |

| R24h | RAM Write data<br>Mask(2) | 0    | 1  | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0           | 0          | 0           | WM1<br>7(0) | WM1<br>6(0) | WM1<br>5(0) | WM1<br>4(0) | WM1<br>3(0) | WM1<br>2(0) |

: Setting disable

| Reg. | Register                           | R/W   | RS |             |             |             | Upper        | Code         | )            |              |              |             |             |             | Lower       | Code         | )            |              |              |

|------|------------------------------------|-------|----|-------------|-------------|-------------|--------------|--------------|--------------|--------------|--------------|-------------|-------------|-------------|-------------|--------------|--------------|--------------|--------------|

| No.  | Register                           | IN/VV | KS | RB15        | RB14        | RB13        | RB12         | RB11         | RB10         | RB9          | RB8          | RB7         | RB6         | RB5         | RB4         | RB3          | RB2          | RB1          | RB0          |

| R30h | $\gamma$ Control(1)                | 0     | 1  | 0           | 0           | 0           | 0            | 0            | PKP1<br>2(0) | PKP1<br>1(0) | PKP1<br>0(0) | 0           | 0           | 0           | 0           | 0            | PKP0<br>2(0) | PKP0<br>1(0) | PKP0<br>0(0) |

| R31H | $\gamma$ Control(2)                | 0     | 1  | 0           | 0           | 0           | 0            | 0            | PKP3<br>2(0) | PKP3<br>1(0) | PKP3<br>0(0) | 0           | 0           | 0           | 0           | 0            | PKP2<br>2(0) | PKP2<br>1(0) | PKP2<br>0(0) |

| R32h | $\gamma$ Control(3)                | 0     | 1  | 0           | 0           | 0           | 0            | 0            | PKP4<br>2(0) | PKP4<br>1(0) | PKP4<br>0(0) | 0           | 0           | 0           | 0           | 0            | PKP4<br>2(0) | PKP4<br>1(0) | PKP4<br>0(0) |

| R33h | $\gamma$ Control(4)                | 0     | 1  | 0           | 0           | 0           | 0            | 0            | PRP<br>12(0) | PRP1<br>1(0) | PRP<br>10(0) | 0           | 0           | 0           | 0           | 0            | PRP<br>02(0) | PRP<br>01(0) | PRP 00(0)    |

| R34h | $\gamma$ Control(5)                | 0     | 1  | 0           | 0           | 0           | 0            | 0            | PKN<br>12(0) | PKN1<br>1(0) | PKN<br>10(0) | 0           | 0           | 0           | 0           | 0            | PKN<br>02(0) | PKN<br>01(0) | PKN<br>00(0) |

| R35h | $\gamma$ Control(6)                | 0     | 1  | 0           | 0           | 0           | 0            | 0            | PKN<br>32(0) | PKN<br>31(0) | PKN<br>30(0) | 0           | 0           | 0           | 0           | 0            | PKN<br>22(0) | PKN<br>21(0) | PKN<br>20(0) |

| R36h | $\gamma$ Control(7)                | 0     | 1  | 0           | 0           | 0           | 0            | 0            | PKN<br>52(0) | PKN<br>51(0) | PKN<br>50(0) | 0           | 0           | 0           | 0           | 0            | PKN<br>42(0) | PKN<br>41(0) | PKN<br>40(0) |

| R37h | $\gamma$ Control (8)               | 0     | 1  | 0           | 0           | 0           | 0            | 0            | PRN<br>12(0) | PRN1<br>1(0) | PRN<br>10(0) | 0           | 0           | 0           | 0           | 0            | PRN<br>02(0) | PRN<br>01(0) | PRN<br>00(0) |

| R38h | $\gamma$ Control (9)               | 0     | 1  |             |             |             | VRP<br>14(0) | VRP<br>13(0) | VRP<br>12(0) | VRP1<br>1(0) | VRP<br>10(0) |             |             |             |             | VRP<br>03(0) | VRP<br>02(0) | VRP<br>01(0) | VRP<br>00(0) |

| R39h | $\gamma$ Control (10)              | 0     | 1  |             |             |             | VRN<br>14(0) | VRN<br>13(0) | VRN<br>12(0) | VRN1<br>1(0) | VRN<br>10(0) |             |             |             |             | VRN<br>03(0) | VRN<br>02(0) | VRN<br>01(0) | VRN<br>00(0) |

| R40h | Gate Scan Start<br>Position        | 0     | 1  | 0           | 0           | 0           | 0            | 0            | PRP<br>12(0) | PRP1<br>1(0) | PRP<br>10(0) | 0           | 0           | 0           | 0           | 0            | PRP<br>02(0) | PRP<br>01(0) | PRP 00(0)    |

| R41h | Vertical Scroll<br>Control         | 0     | 1  | 0           | 0           | 0           | 0            | 0            | 0            | 0            | 0            | VL7<br>(0)  | VL6<br>(0)  | VL5<br>(0)  | VL4<br>(0)  | VL3<br>(0)   | VL2<br>(0)   | VL1<br>(0)   | VL0<br>(0)   |

| R42h | First Screen Driving position      | 0     | 1  | SE17<br>(0) | SE16<br>(0) | SE15<br>(0) | SE14<br>(0)  | SE13<br>(0)  | SE12<br>(0)  | SE11<br>(0)  | SE10<br>(0)  | SS17<br>(0) | SS16<br>(0) | SS15<br>(0) | SS14<br>(0) | SS13<br>(0)  | SS12<br>(0)  | SS11<br>(0)  | SS10<br>(0)  |

| R43h | Second Screen Driving Position     | 0     | 1  | SE27<br>(0) | SE26<br>(0) | SE25<br>(0) | SE24<br>(0)  | SE23<br>(0)  | SE22<br>(0)  | SE21<br>(0)  | SE20<br>(0)  | SS27<br>(0) | SS26<br>(0) | SS25<br>(0) | SS24<br>(0) | SS23<br>(0)  | SS22<br>(0)  | SS21<br>(0)  | SS20<br>(0)  |

| R44h | Horizontal RAM<br>Address Position | 0     | 1  | HEA<br>7(0) | HEA<br>6(0) | HEA<br>5(0) | HEA<br>4(0)  | HEA<br>3(0)  | HEA<br>2(0)  | HEA<br>1(0)  | HEA<br>0(0)  | HAS<br>7(0) | HAS<br>6(0) | HAS<br>5(0) | HAS<br>4(0) | HAS<br>3(0)  | HAS 2(0)     | HAS<br>1(0)  | HAS 0(0)     |

| R45h | Vertical RAM<br>Address Position   | 0     | 1  | VEA7<br>(0) | VEA6<br>(0) | VEA5<br>(0) | VEA4<br>(0)  | VEA3<br>(0)  | VEA2<br>(0)  | VEA1<br>(0)  | VEA0<br>(0)  | VAS<br>7(0) | VAS<br>6(0) | VAS<br>5(0) | VAS<br>4(0) | VAS<br>3(0)  | VAS<br>2(0)  | VAS<br>1(0)  | VAS<br>0(0)  |

: Setting disable

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

# 7.4 Instruction Explanation

|               |     |               |                | Input Parts                                                                                                                                                                                                                   |

|---------------|-----|---------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signals       | I/O | Pin<br>Number | Connected with | Description                                                                                                                                                                                                                   |

| IM3-1,<br>IM0 | ı   | 4             | VSSD/<br>IOVcc | Select the MPU interface mode as listed below   IMO(ID)   IM1   IM2   IM3   MPU interface mode   DB pins                                                                                                                      |

| NCS           | ı   | 1             | MPU            | like the ID setting for the device code in transfer data.  Chip select signal. Low: chip can be accessed; High: chip cannot be accessed. Must be connected to VSSD if not in use.                                             |

| VLD           |     | 1             | MPU            | Fix to VSSD                                                                                                                                                                                                                   |

| RS            | 1   | 1             | MPU            | The signal for register index or register command select. Low: Register index or internal status (in read operation); High: Register command. Connect to IOVcc or VSSD level when serial data transfer interface is selected. |

| E_NWR         | ı   | 1             | MPU            | Serves as a write signal and writes data at the rising edge in i80 system interface.  Serves as the synchronous clock signal in serial data transfer interface.                                                               |

| RW_NRD        | ı   | 1             | MPU            | Low: Write: High: Read) Serves as a read signal and reads data at the low level in i80 system interface. Fix it to IOVcc or VSSD level when using serial data transfer interface.                                             |

| ENABLE        | 1   | 1             | MPU            | A data ENABLE signal in RGB I/F mode. Fix the unused pin to either the VSSD level or the IOVcc level. Low: Selected (access enabled) The polarity of the ENABLE signal is inverted by the EPL bit.    EPL                     |

| VSYNC         | ı   | 1             | MPU            | Frame's ynchronizing signal. Fix to the IOVcc level when not used.  If VSPL=0: Active low.  If VSPL=1: Active high.                                                                                                           |

| HSYNC         | ı   | 1             | MPU            | Frame synchronizing signal. Fix to the IOVcc level when not used. If HSPL=0: Active low. If HSPL=1: Active high.                                                                                                              |

| DOTCLK        | ı   | 1             | MPU            | Dot clock signal. Fix to the IOVcc level when not used. If DPL=0: Data are input on the rising edge of DOTCLK. If DPL=1: Data are input on the falling edge of DOTCLK.                                                        |

| PD0~17        | ı   | 18            | MPU            | An 18-bit bus RGB data bus in 80-system interface mode. Fix the unused pins to either the VSSD level or the IOVcc level. 6-bit bus: use PD17-PD12 16-bit bus: use PD17-PD13 and PD11-PD1 18-bit bus: use PD17-PD0             |

|         |     |               |                                 | Input Parts                                                                                                                                                                                                                                                                      |

|---------|-----|---------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signals | 1/0 | Pin<br>Number | Connected with                  | Description                                                                                                                                                                                                                                                                      |

| NRESET  | I   | 1             | MPU or reset<br>circuit         | Reset pin. Setting either pin low initializes the LSI. Must be reset after power is supplied.                                                                                                                                                                                    |

| VcomR   | ı   | 1             | Variable<br>Resistor or<br>open | A VoomH reference voltage. When adjusting VoomH externally, set registers to halt the VoomH internal adjusting circuit and place a variable resistor between VGAM1OUT and VSSD. Otherwise, leave this pin open and adjust VoomH by setting the internal register of the HX8306A. |

| Vci1    | Ι   | 1             | VciOUT                          | A reference voltage for the step-up circuit1. Connect to an external power supply of 2.75V of less when not using an internal reference voltage.                                                                                                                                 |

| VLCD    | _   | 1             | VLCDC                           | A power supply for the source driver outputs. A reference voltage for the<br>step-up circuit2                                                                                                                                                                                    |

| VGH     | _   | 1             | VGHC                            | A power supply for the TFT LCD's gate driver. Connect to VGHC.                                                                                                                                                                                                                   |

| VGL     | _   | 1             | VGLC                            | A power supply for the TFT LCD's gate driver. Connect to VGLC.                                                                                                                                                                                                                   |

| VCL     | _   | 1             | VCLC                            | A power supply for the VoomL level. Connect to VCLC.                                                                                                                                                                                                                             |

| TEST1   |     | 1             | VSSD                            | A test pin. Make sure to fix it to the VSSD level.                                                                                                                                                                                                                               |

| TEST2   |     | 1             | VSSD                            | A test pin. Make sure to fix it to the VSSD level.                                                                                                                                                                                                                               |

| VGS     | I   | 1             | VSSD or<br>external<br>resistor | Connect to a variable resistor to adjusting internal gamma reference voltage for matching the characteristic of different panel used.                                                                                                                                            |

| Vci     | Ι   | 1             | Power supply                    | For analog power supply. Connect to an external power supply 2.5V~3.3V.                                                                                                                                                                                                          |

| VciLVL  | I   | 1             | Power<br>Supply                 | Generates a reference voltage (VciOUT, REGP) from the VciLVL level<br>according to the ratio determined by the VC2-0 BITS. Connect to Vci on<br>the FPC.                                                                                                                         |

|                        |     |               |                                       | Input/Output Part                                                                                                                                                                                                                                                                                                                                   |

|------------------------|-----|---------------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signals                | I/O | Pin<br>Number | Connected with                        | Description                                                                                                                                                                                                                                                                                                                                         |

| C11A,C11B              | I/O | 2             | Step-up<br>Capacitor                  | Connect to the step-up capacitors according to the step-up factor. Leave this pin open if the internal step-up circuit is not used.                                                                                                                                                                                                                 |

| C21A,C21B<br>C22A,C22B | I/O | 6             | Step-up<br>Capacitor                  | Connect these pins to the capacitors for the step-up circuit 2. According to the step-up rate. When not using the step-up circuit2, disconnect them.                                                                                                                                                                                                |

| OSC1,OSC2              | I/O | 2             | Oscillation<br>Resistor               | Connect an external resistor for generating internal clock by internal R-C oscillation. Or an external clock signal is supplied through OSC1 with OSC2 open.                                                                                                                                                                                        |

| DB0_S DI               | I/O | 1             | MPU                                   | Operates liked an 18-bit bi-directional data bus. 8-bits bus I/F: DB17-10 9-bits bus I/F: DB17-9 16-bits bus I/F: DB17-10, 8-1 18-bits bus I/F: DB17-0 Connected unused pins to the IOVcc or VSSD level. When Serial Data Input pin in Serial Data Transfer interface. The input data is latched by the rising edge of the SCL signal on the chip.  |

| DB1_SDO                | I/O | 1             | MPU                                   | Operates liked an 18-bit bi-directional data bus. 8-bits bus I/F: DB17-10 9-bits bus I/F: DB17-9 16-bits bus I/F: DB17-10, 8-1 18-bits bus I/F: DB17-0 Connected unused pins to the IOVcc or VSSD level. When Serial Data Output pin in Serial Data Transfer interface. The data is output by the falling edge of the SCL signal on the chip.       |

| DB2~17                 | I/O | 16            | MPU                                   | Operates liked a 18-bit bi-directional data bus 8-bit bus: use DB8-DB1 9-bit bus: use DB8-DB0 16-bit bus: use DB17-DB10 and DB8-DB1 18-bit bus: use DB17-DB0 Connected unused pins to the IOVcc or VSSD level.                                                                                                                                      |

| REGP                   | I/O | 1             | Test pin                              | A test pin for VGAM1OUT. Disconnect it.                                                                                                                                                                                                                                                                                                             |

| VGAM1OUT               | I/O | 1             | Stabilizing capacitor or power supply | A reference voltage for VGAM2 between VSSD and VLCD from the reference voltage between Vci and VSSD that is generated internally. VGAM1OUT serves as a source driver grayscale reference voltage VGAM2, a VcomH level reference voltage, and a Vcom amplitude reference voltage. Connect to a stabilizing capacitor. VGAM1OUT = 3.0 ~ (VLCD – 0.5)V |

| VTESTS                 | I/O | 1             | Open                                  | A test pin. Disconnect it.                                                                                                                                                                                                                                                                                                                          |

| TVCOMHI                | I/O | 1             | Open                                  | A test pin for VcomH. Disconnect it.                                                                                                                                                                                                                                                                                                                |

| TVCOMLI                | I/O | 1             | Open                                  | A test pin for VcomL. Disconnect it.                                                                                                                                                                                                                                                                                                                |

| TVMAG                  | I/O | 1             | Open                                  | A test pin for VcomL. Disconnect it.                                                                                                                                                                                                                                                                                                                |

| TESTO1~4               | -   | 4             | -                                     | Dummy pads. Disconnect them.                                                                                                                                                                                                                                                                                                                        |

| DUMMY1,2,13            | -   | 3             | -                                     | Dummy pads. Disconnect them.                                                                                                                                                                                                                                                                                                                        |

| DUMMY3-12,14-<br>19    | -   | 16            | -                                     | Dummy pads. Can be connected to the wiring to the COG panel.                                                                                                                                                                                                                                                                                        |

| DUMMYR1-9              | -   | 9             | -                                     | Dummy pads. Available for measuring the COG contact resistance. DUMMYR1 and DUMMYR2 are short-circuited within the chip. DUMMYR3, DUMMYR4 and DUMMYR5 are short-circuited within the chip. DUMMYR6, DUMMYR7, DUMMYR8, and DUMMYR9 are short circuited within the chip.                                                                              |

| VGLDUM1~4              | -   | 4             | -                                     | Outputs the internal VGL level. Use as dummy gate output pins.                                                                                                                                                                                                                                                                                      |

|                        |     |               |                                       | Input/Output Part                                                                                                                                                                                                                                                                                                                                                      |

|------------------------|-----|---------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signals                | I/O | Pin<br>Number | Connected with                        | Description                                                                                                                                                                                                                                                                                                                                                            |

| C11A,C11B              | I/O | 2             | Step-up<br>Capacitor                  | Connect to the step-up capacitors according to the step-up factor. Leave this pin open if the internal step-up circuit is not used.                                                                                                                                                                                                                                    |

| C21A,C21B<br>C22A,C22B | I/O | 6             | Step-up<br>Capacitor                  | Connect these pins to the capacitors for the step-up circuit 2. According to the step-up rate. When not using the step-up circuit2, disconnect them.                                                                                                                                                                                                                   |

| OSC1,OSC2              | I/O | 2             | Oscillation<br>Resistor               | Connect an external resistor for generating internal clock by internal R-C oscillation. Or an external clock signal is supplied through OSC1 with OSC2 open.                                                                                                                                                                                                           |

| DB0_S DI               | I/O | 1             | MPU                                   | Operates liked an 18-bit bi-directional data bus. 8-bits bus I/F: DB17-10 9-bits bus I/F: DB17-9 16-bits bus I/F: DB17-10, 8-1 18-bits bus I/F: DB17-0 Connected unused pins to the IOVcc or VSSD level. When Serial Data Input pin in Serial Data Transfer interface. The input data is latched by the rising edge of the SCL signal on the chip.                     |

| DB1_SDO                | I/O | 1             | MPU                                   | Operates liked an 18-bit bi-directional data bus. 8-bits bus I/F: DB17-10 9-bits bus I/F: DB17-9 16-bits bus I/F: DB17-10, 8-1 18-bits bus I/F: DB17-0 Connected unused pins to the IOVcc or VSSD level. When Serial Data Output pin in Serial Data Transfer interface. The data is output by the falling edge of the SCL signal on the chip.                          |

| DB2~17                 | I/O | 16            | MPU                                   | Operates liked a 18-bit bi-directional data bus 8-bit bus: use DB8-DB1 9-bit bus: use DB8-DB0 16-bit bus: use DB17-DB10 and DB8-DB1 18-bit bus: use DB17-DB0 Connected unused pins to the IOVcc or VSSD level.                                                                                                                                                         |

| REGP                   | I/O | 1             | Test pin                              | A test pin for VGAM1OUT. Disconnect it.                                                                                                                                                                                                                                                                                                                                |

| VGAM1OUT               | I/O | 1             | Stabilizing capacitor or power supply | A reference voltage for VGAM2 between VSSD and VLCD from the reference voltage between Vci and VSSD that is generated internally. VGAM1OUT serves as a source driver grayscale reference voltage VGAM2, a VcomH level reference voltage, and a Vcom amplitude reference voltage. Connect to a stabilizing capacitor. VGAM1OUT = $3.0 \sim (\text{VLCD} - 0.5)\text{V}$ |

| VTESTS                 | I/O | 1             | Open                                  | A test pin. Disconnect it.                                                                                                                                                                                                                                                                                                                                             |

| TVCOMHI                | 1/0 | 1             | Open                                  | A test pin for VcomH. Disconnect it.                                                                                                                                                                                                                                                                                                                                   |

| TVCOMLI                | I/O | 1             | Open                                  | A test pin for VcomL. Disconnect it.                                                                                                                                                                                                                                                                                                                                   |

| TVMAG                  | I/O | 1             | Open                                  | A test pin for VcomL. Disconnect it.                                                                                                                                                                                                                                                                                                                                   |

| TESTO1~4               | -   | 4             | -                                     | Dummy pads. Disconnect them.                                                                                                                                                                                                                                                                                                                                           |

| DUMMY1,2,13            | -   | 3             | -                                     | Dummy pads. Disconnect them.                                                                                                                                                                                                                                                                                                                                           |

| DUMMY3-12,14-<br>19    | -   | 16            | -                                     | Dummy pads. Can be connected to the wiring to the COG panel.                                                                                                                                                                                                                                                                                                           |

| DUMMYR1-9              | -   | 9             | -                                     | Dummy pads. Available for measuring the COG contact resistance. DUMMYR1 and DUMMYR2 are short-circuited within the chip. DUMMYR3, DUMMYR4 and DUMMYR5 are short-circuited within the chip. DUMMYR6, DUMMYR7, DUMMYR8, and DUMMYR9 are short circuited within the chip.                                                                                                 |

| VGLDUM1~4              | -   | 4             | -                                     | Outputs the internal VGL level. Use as dummy gate output pins.                                                                                                                                                                                                                                                                                                         |

|          |        |               |                       | Power Part                                                                                                                                                                                |

|----------|--------|---------------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signals  | I/O    | Pin<br>Number | Connected with        | Description                                                                                                                                                                               |

| Vcc      | -      | 1             | Power supply          | A power supply for the internal logic. VCC = 2.4 ~ 3.3V                                                                                                                                   |

| IOVcc    | -      | 1             | Power supply          | Power supply for internal core logic when VDC is disabled. Voltage range: 1.65 ~ 3.3V if VDC is disabled. Tie together with VCC if VDC is enabled.                                        |

| VSSA     | -      | 1             | Power supply          | Analogy ground. VSSA = 0V. When using the COG method, connect to VSSD on the FPC to prevent noise.                                                                                        |

| VSSD     | -      | 1             | Power supply          | Ground for the internal RAM. VSSD = 0V. When using the COG method, connect to VSSD on the FPC to prevent noise.                                                                           |

| V0P,V61P | I or O | 2             | Stabilizing capacitor | Outputs from the internal positive polarity operational amplifier when it is on (when SAP2-0 = "001", "010", "011", "100", and "101"). Connect to a capacitor to stabilize the amplifier. |

| V0N,V61N | I or O | 2             | Stabilizing capacitor | Outputs from the internal negative polarity operational amplifier when it is on (when SAP2-0 = "001", "010", "011", "100", and "101"). Connect to a capacitor to stabilize the amplifier  |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

### 7.5 Reset Function

If the /RESET input becomes L or the reset command is input, the internal timing generator is initialized. Must be reset after the power is supplied. The time required for the /RESET input is at least 1ms. When the power supply is reset while the power supply is ON, wait at least 10ms after the power has been supplied until the RC oscillation frequency become stabilized. While waiting, do not make initial settings for the instruction set, nor access to the GRAM.

| Register                        | Initial State of Instructions                                                                                                          |

|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|

| Start oscillation               | Executed                                                                                                                               |

| Driver output control           | NL4-0="10101", SS="0", CS="0"                                                                                                          |

| LCD driving AC control          | FLD1-0="01", B/C="0", EOR=0, NW5-0="00000"                                                                                             |

| Dower control (4)               | BT2-0="000", DC2-0="000", AP2-0="000" : LCD power off,                                                                                 |

| Power control (1)               | SLP="0", STB="0" : Standby mode off                                                                                                    |

| Power control (2)               | CAD="0", VRN4-0="00000", VRL-4="00000"                                                                                                 |

| Power control (3)               | VC2-0="000"                                                                                                                            |

| Power control (4)               | VRL3-0="0000", PON="0", VRH-3="0000"                                                                                                   |

| Power control (5)               | VCOMG="0", VDV4-0="00000", VCM4-0="00000"                                                                                              |

| Entry mode set                  | HWM="0", I/D-0="11" : Increment by 1,                                                                                                  |

| Entry mode set                  | AM="0" : Horizontal move, LG2-0="0" : Replace mode                                                                                     |

| Compare register                | CP17-0:00000h                                                                                                                          |

| Display control                 | PT1-0="00", VLE2-1="00" : No vertical scroll, SPT="0", GON="0", DTE="0", CL="0" :262,144-color mode, REV="0", D1-0="000" : Display off |

| Frame cycle control             | GD1-0="00", SDT1-0="00", CE1-0="00": No equalization, DIV1-0="00": 1 divided clock, RTN3-0="0000": 16 clock in 1H period               |

| Gate scan starting position     | SCN4-0="00000"                                                                                                                         |

| Vertical scroll                 | VC7-0="0000 0000"                                                                                                                      |

| 1 <sup>st</sup> screen division | SE17-10="1111 1111", SS17-10= "0000 0000"                                                                                              |

| 2 <sup>nd</sup> screen division | SE27-20="1111 1111", SS27-20="0000 0000"                                                                                               |

| Horizontal RAM address position | HEA7-0="1000 0011", HSA7-0="0000 0000"                                                                                                 |

| Register                      | Initial State of Instructions                                                                                                                                                                                                                                                                                             |

|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Vertical RAM address position | VEA7-0="1010 1111", VSA7-0="0000 0000"                                                                                                                                                                                                                                                                                    |

| RAM write data mask           | WM15-0="0000H" : No mask                                                                                                                                                                                                                                                                                                  |

| RAM address set               | AD15-0= "0000H"                                                                                                                                                                                                                                                                                                           |

| Gamma control                 | MP02-00="000", MP12-10="000",MP22-20="000", MP32-30="000"<br>MP42-40="000", MP52-50="000", MP02-00="000", MP12-10="000"<br>MN02-00="000", MN12-10="000", MN22-20="000", MN32-30="000"<br>MN42-40="000", MN52-50="000", CN02-00="000", CN12-10="000"<br>OP14-10="00000", OP02-00="0000", ON14-10="00000",<br>ON03-00="000" |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

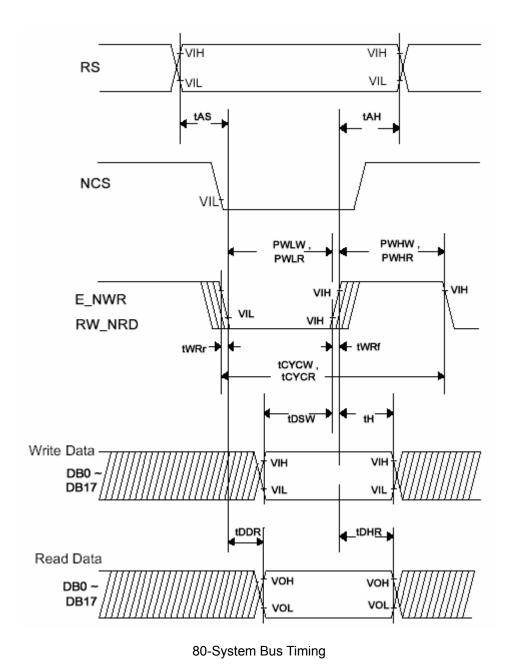

# **8 Timing Characteristics**

# 9.1Timing Characteristics

Read / Write Characteristics (8080-series MPU)

**Bus Timing Characteristics**

<<Normal Write Mode(HWM=0),loVcc=1.65V-2.4V>>

|                      | Item                        | ,     | Symbol   | Unit | Min | Тур | Max |

|----------------------|-----------------------------|-------|----------|------|-----|-----|-----|

| Bus cycle time       |                             | Write | tCYCW    | ns   | 250 | -   |     |

| Bus Cycle time       | ;                           | Read  | tCYCR    | ns   | 500 | -   |     |

| Write low-leve       | l pulse width               |       | PWLW     | ns   | 100 | -   | -   |

| Read low-leve        | I pulse width               |       | PWLR     | ns   | 250 | -   | -   |

| Write high-leve      | el pulse width              |       | PWHW     | ns   | 110 | -   | -   |

| Read high-leve       | Read high-level pulse width |       | PWHR     | ns   | 200 | -   | -   |

| Write/Read ris       | e/fall time                 |       | tWRr,WRf | ns   |     | -   | 25  |

| Set up time          | (RS to NCS,E                | _NWR) | tAS      | ns   | 0   | -   |     |

| Set up time          | (RS toNCS,RE                | _NRD) | iAS      | ns   | 10  | -   | -   |

| Address hold t       | ime                         |       | tAH      | ns   | 2   | -   | -   |

| Write data set       | up time                     |       | tDSW     | ns   | 25  | -   | -   |

| Write data hold time |                             | tH    | ns       | 10   | -   | -   |     |

| Read data delay time |                             |       | tDDR     | ns   |     | -   | 200 |

| Read data hole       | d time                      |       | tDHR     | ns   | 10  | -   | -   |

### <<High-Speed Write Mode(HWM=1),Vcc1.8V-2.4V>>

| Item                         |                             | Symbol   | Unit | Min | Тур | Max |

|------------------------------|-----------------------------|----------|------|-----|-----|-----|

| Pue avale time               | Write                       | tCYCW    | ns   | 100 | -   |     |

| Bus cycle time               | Read                        | tCYCR    | ns   | 500 | -   |     |

| Write low-level pulse width  |                             | PWLW     | ns   | 30  | -   | -   |

| Read low-level pulse width   |                             | PWLR     | ns   | 250 | -   | -   |

| Write high-level pulse width |                             | PWHW     | ns   | 40  | -   | -   |

| Read high-level pulse width  | Read high-level pulse width |          | ns   | 200 | -   | -   |

| Write/Read rise/fall time    |                             | tWRr,WRf | ns   | ı   | -   | 25  |

| Set up time (RS to CS*       | ,WR*)                       | tAS      | ns   | 0   | -   |     |

| (RS to RD*                   | ·)                          | 1/3      | ns   | 10  | -   | -   |

| Address hold time            |                             | tAH      | ns   | 2   | -   | -   |

| Write data set up time       | tDSW                        | ns       | 25   | -   | -   |     |

| Write data hold time         | tH                          | ns       | 10   | -   | -   |     |

| Read data delay time         | tDDR                        | ns       | ı    | -   | 200 |     |

| Read data hold time          |                             | tDHR     | ns   | 10  | -   | -   |

The contents of this document are confidential and must not be disclosed wholly or in part to any third part without the prior written consent of AMPIRE CO., LTD

### <<Normal Write Mode(HWM=0),loVcc = 2.4V-3.3V>>

|                        | Item           | ,      | Symbol   | Unit | Min | Тур | Max |

|------------------------|----------------|--------|----------|------|-----|-----|-----|

| Bus cycle time         |                | Write  | tCYCW    | ns   | 100 | -   |     |

| bus cycle time         | ;              | Read   | tCYCR    | ns   | 500 | -   |     |

| Write low-leve         | l pulse width  |        | PWLW     | ns   | 40  | -   | -   |

| Read low-leve          | I pulse width  |        | PWLR     | ns   | 250 | -   | -   |

| Write high-leve        | el pulse width |        | PWHW     | ns   | 30  | -   | -   |

| Read high-leve         | el pulse width |        | PWHR     | ns   | 200 | -   | -   |

| Write/Read ris         | e/fall time    |        | tWRr,WRf | ns   | -   | -   | 25  |

| Set up time            | (RS to NCS,E   | _NWR)  | tAS      | ns   | 0   | -   |     |

| Set up time            | (RS toNCS,RE   | E_NRD) | iAS      | ns   | 10  | -   | -   |

| Address hold t         | ime            |        | tAH      | ns   | 2   | -   | -   |

| Write data set up time |                |        | tDSW     | ns   | 25  | -   | -   |

| Write data hold time   |                |        | tH       | ns   | 10  | -   | -   |

| Read data delay time   |                |        | tDDR     | ns   | -   | -   | 200 |

| Read data hole         | d time         |        | tDHR     | ns   | 10  | -   | -   |

### <<High-Speed Write Mode(HWM=1),Vcc = 2.4V-3.3V >>